|

Realisierung und Meßwerte des Mischers

Die Realisierung

|

Analog Schalter 4066, 4016

Invertierer 74HCT04 oder über 4066 invertieren

Das Rechtecksignal des Carriers schaltet abwechseln den einen oder anderen analogen Schalter durch, somit kommt entweder das Signal selbst bzw. das invertierte Signal zum Ausgang.

Generierung des Carriers

|

Berechnung der benötigten Timerregister: Timermode ist Mode 7, also PWM (Pulsweitenmodulation). Periodendauer soll 1/62kHz sein. Hierzu muß das Timer Load Register (TLR) beschrieben werden,

ergibt sich

somit ergibt sich eine Frequenz von 61,982kHz.

Um einen Duty von 0.5 zu bekommen (also Thi = T low) muß noch TCPR (Timer Compare Register) berechnet werden, welches den Zählstand enthält ab dem der Ausgang getoggelt wird.

Aus der Formel, die man auch im Handbuch des DSP findet, ergibt sich

Diese Werte sind rein rechnerisch ermittelt und dienen als erste Näherung. Die genaue Einstellung nimmt man mittels des Oszilloskopes vor. Nun muß nur noch der Modus initialisiert und der Timer gestartet werden. Hierzu muß das Timer Control Status Register beschrieben werden.

Die Bedeutung der einzelnen Bits können dem Handbuch entnommen werden.

Die Implementierung

|

move $FFFCE7,a1

move a1,x:#M_TLR1

move $FFFE74,a1

move a1,x:#M_TCPR

move $217,a1

move a1,x:#M_TCSR1

Um den 3,3V Pegel des DSPs an den benötigten 5V Pegel der CMOS Bausteine anzupassen wird der Carrier über einen Pegelumsetzer eingekoppelt (Emitterschaltung).

Der Schaltungsentwurf

|

Bemerkung:

BP: Bandpaß mit Einfachmitkopplung, Quelle: Tietze, Schenk, Halbleiter Schaltungstechnik, 11. Auflage.

Mit dem 50k Poti kann man f0 einstellen, mit dem 2k Poti die Güte/Verstärkung, wobei bei dieser Anordnung die Güte nicht unbedingt getrennt von der f0 eingestellt werden kann, da Bauteiltoleranzen ins Gewicht fallen können. Die Güte ist so einzustellen, das die maximal auftretende Amplituden nicht größer als 2V sind, um den CMOS 4066 nicht zu zerstören. (Zusätzliche Schutzmaßnahme wären Dioden jeweils gegen Masse und +5V an den 2k Spannungsteilern, die die Spannung begrenzen)

Der TP am Ausgang ist fest auf eine Eckfrequenz von etwa 16kHz dimensioniert. Der 10k Widerstand am Ausgang dient als Lastwiderstand. Carrier IN, Signal_IN und Signal_OUT sind auf Masse bezogen. Den Invertierer 74HCT04 hätte man sich sparen können, wenn man einen noch freien analogen Schalter auf dem 4066 als Invertierer geschaltet hätte.

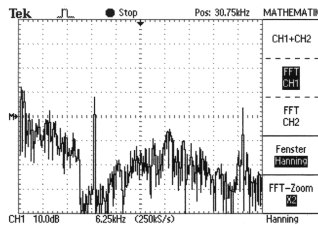

Die Meßergebnisse

|

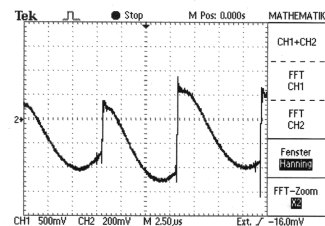

Signal am Mischerausgang (Zerhacker)

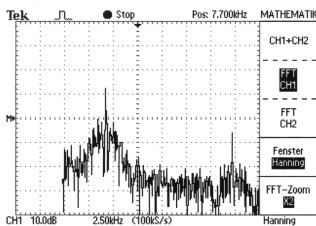

Heruntergemischtes RDS-Signal bei 5kHz (Ausgangssignal der analogen Vorverarbeitung):

Danksagung

|

Thomas Heberlein, ET 7 MM (WS 1999/2000).

|